频率源中其余元件简介

设计中频率源通过一个锁相环路产生,除了上节介绍的ADF4159外,还有另外几个主要元件。

CY7C68013A介绍

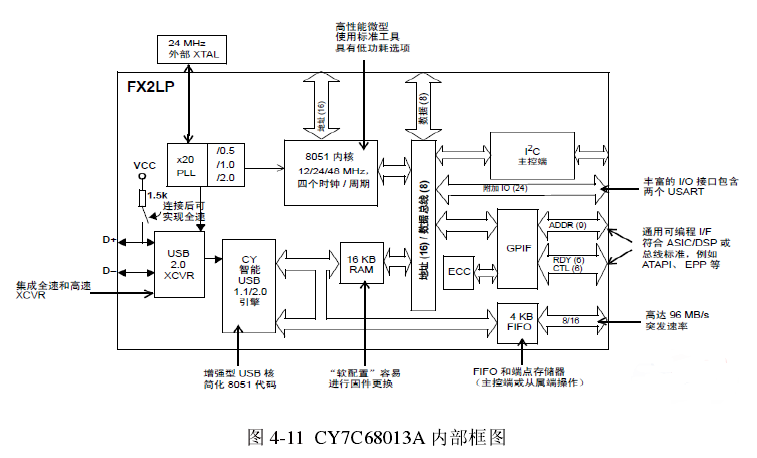

如 图 4-11 所 示 为 CY7C68013A 内 部 框 图 , CY7C68013A 是 Cypress 公 司 的EZ-USB FX2LP系列低功耗版本单片机,具有和8051兼容的CPU和指令系统,同时包括USB接口和完整的USB 2.0协议引擎,并且提供了完善的固件及主机程序开发包。该单片机的CPU采用的是增强型8051内核,比标准的8051的速度快,硬件资源更为丰富,功能更强大。在此,CY7C68013A作为PC端对于ADF4159的USB连接与控制系统。

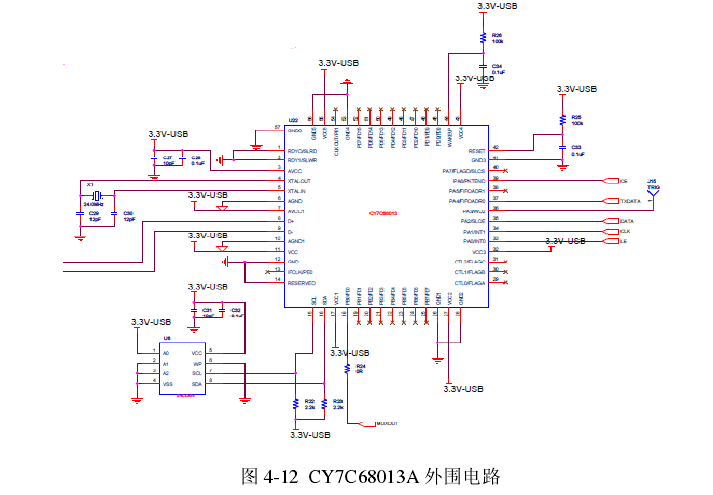

根据CY7C68013A的数据表,根据它在此设计中的应用对其外围电路进行设计,如图4-12为利用Or CAD软件对其外围电路进行的设计。

压控振荡器HMC739LP4介绍

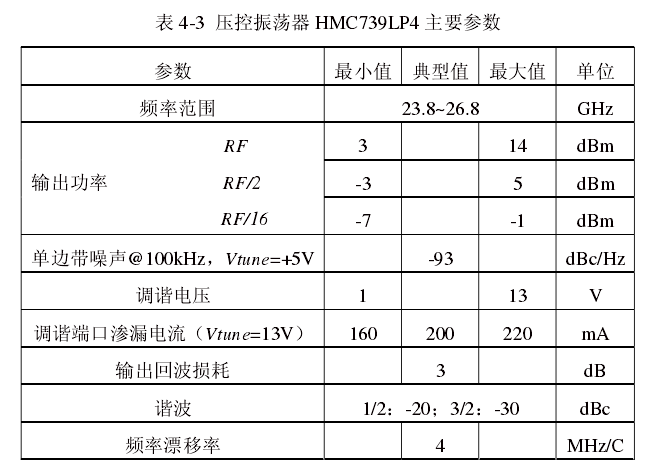

在设计中压控振荡器的选择要保证锁相环输出频率的要求,在这里压控振荡器(VCO)选择Hittite公司的HMC739LP4,输出频率为23.8GHz~26.8GHz.,其有RF、RF/2、RF/16三个输出端口。如表4-3为其主要特性参数:

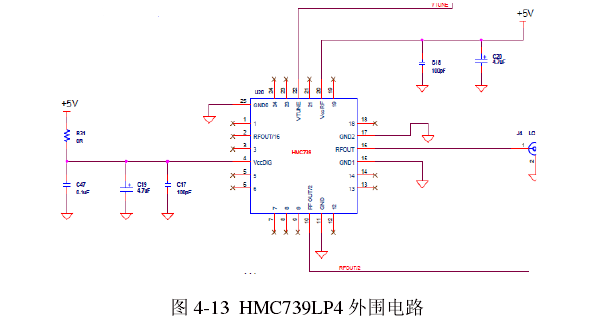

根据HMC739LP4数据表对其外围电路进行设计,如图4-13所示。

在此设计中,利用了HMC739LP4的RF输出和RF/2输出端口,在锁相环路的设计中省去一个功分器和二分频器。

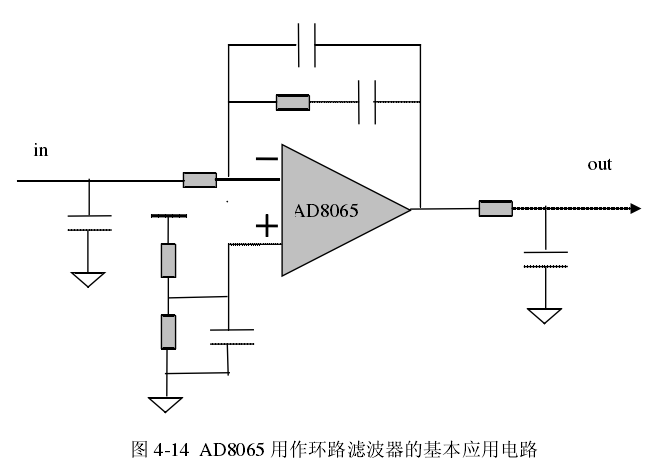

运算放大器AD8065基本介绍AD8065是电压反馈型运算放大器,其电源范围是5V到24V,增益带宽积(GBP)约为145MHz,并具有低噪声特性。该特性使其成为有源滤波器的理想选择。

如图4-14为AD8065的作为环路滤波器的基本应用电路。

方案可行性分析

根据以上几个核心器件的技术指标以及方案结构对频率源要求指标的可行性进行分析,这是最终实现设计的基础。

输出频率分析

系统指标要求的输出频率为24GHz~25GHz,频率步进为20kHz。方案中利用频率合成器ADF4159,该芯片具有线性扫频模式,并有最高13GHz的输入频率,配合带有二分频输出的VCO芯片HMC739LCP4,通过PC控制即可产生24GHz~25GHz,步进20kHz的扫频频率。

由上一节中式(4-4)和(4-5)可计算得到输出频率的分辨率为foeV.aes =faes ×20EV-OF/SET=2.98×21=5.96Hz

线性度分析

该方案利用PLL环路产生线性调频信号,调频信号带宽1GHz,频率步进20kHz,根据调频信号线性度定义,计算得其线性度为2×105,线性度接近理想状态,满足性能指标。

相位噪声分析

在PLL结构频率合成器中,相位噪声根据环路滤波器的带宽可分为带内相位噪声和带外噪声。带外噪声主要来自于VCO,这里VCO选择的是HMC739LCP4,

其偏频100kHz与1MHz处的相位噪声分别为-93dBc/Hz@100kHz和

-120dBc/Hz@1MHz。下面主要分析带内相位噪声。

方案采用的100MHz晶振的相位噪声指标是