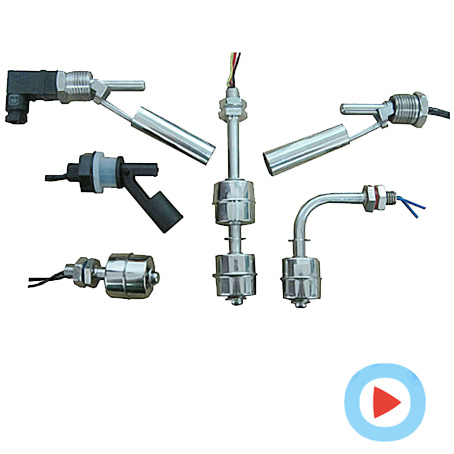

输出功率分析

如图 4-19 为该方案功率流程图,利用它对每一个芯片的功率可行性进行验证。 100MHz 晶振的输出功率为+3d Bm~+6d Bm,满足 ADF4159 参考信号 REFin (-5d Bm~+9dBm)的功率范围,VCO 自带有 RFout 与 RFout/2 输出端口,在指标 要求的频率范围内,RFout 功率为+11.5d Bm,RFout/2 功率为+2d Bm,功分器的损 耗为 6d B,则输入到 ADF4159 的射频功率为-4d Bm,满足其射频输入 RFin (-10d Bm~0dBm)的功率范围,功分器的另一路输出经过二倍频器 HMC448LC3B 的倍频后输出功率为+11d Bm 的 24GHz~25GHz 调频信号。

本章小结

本章首先介绍了 DDS 与 PLL 外混频的频率源方案的设计过程,此方案可以很好的实现设计的要求,但其电路复杂,芯片种类多,成本高,不适合实际应用。据此对方案进行优化,利用新型的 PLL 芯片 ADF4159 重新对频率源进行设计,同样可以方便的实现设计指标,电路更加简单,操作方便,成本也有大幅的降低。