锁相环的主要特性分析

1、PLL 的主要参数

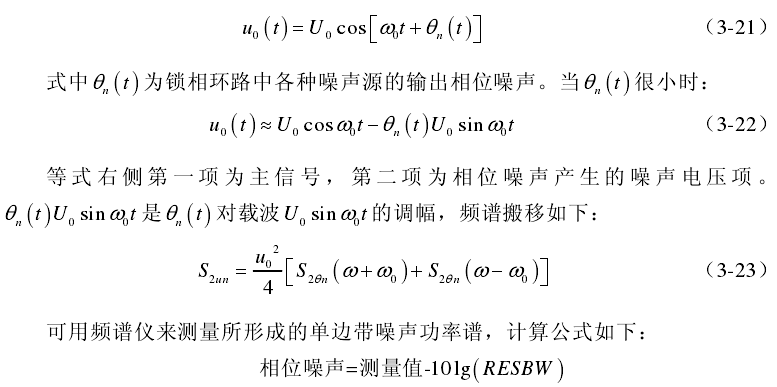

(1) 相位噪声

一个具有相位噪声的信号可以表示为:

2) 杂散

杂散指的是与所需要的输出信号没有谐波关系的那些无用的频率谱。而锁相环路中杂散的产生主要来自鉴相波纹,可通过减小环路带宽或者是另外加滤波器来滤除。

(3) 相位裕量

由于锁相环为闭合环路,即满足闭合环路的自激条件,所以保证一定的相位裕量能够使环路稳定,通常相位裕量不小于 45 度。

(4)锁定时间

锁定时间指的是环路输出从频率fl跳至另一频率f2,从控制变频生效到频率稳定输出花费的时间,它与环路的带宽大小成反比。

(5)捕获

锁相环路在开机频率变更时或从开环至闭环的最初时间内是失锁的,环路经失锁进入到锁定的整个过程称为捕获。

(6)跟踪

环路跟踪的性能指的是环路在锁定状态时,当输入信号的相位变化时,环路输出信号相位随输入信号变化的能力。

2、PLL的捕获性能分析

锁相环中,捕获是指环路从失锁状态通过环路本身的调节作用进入到锁定的状态。失锁的状态下VCO的输出频率并不同于输入的信号频率,同时也不满足误差相位较小的条件,因此分析捕获过程必须采用非线性的分析。在此我们分析捕获特性时有三点是最主要的:环路是怎样从失锁状态到锁定状态的;能保证环路通过本身调节可达到锁定最大的输入频差(捕获带)是多大;从失锁状态到锁定状态需要的时间。捕获带大,捕捉时间短,则说明环路的捕捉性能好。

3、锁相环的稳定性分析

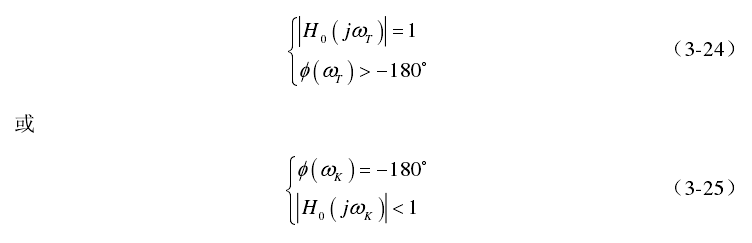

锁相环是基于相位的负反馈系统,它具有极其好的特性。锁相环的稳定性是整个系统能正常工作的必要条件。它的稳定性与振荡器一样,当锁相环闭环系统处于平衡的锁定状态时,在外界噪声、干扰等因素的作用下,若环路有能力来保持它的平衡状态,则环路是稳定的,否则是不稳定的。我们选择波特准则作为判定系统稳定性的标准,稳定条件为

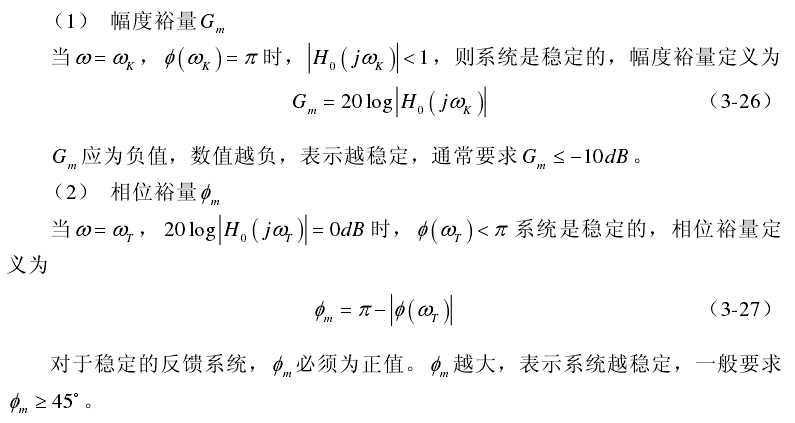

式中,Ho(jw)是开环传递函数;a是开环增益为1时对应的角频率,称为增益临界频率;ax是开环相移为x时对应的角频率,称为相位临界频率。当时,系统会处于临界状态。而系统稳定只是环路正常工作的必要条件,为了加强环路的稳定性,需设计出一定的稳定裕量,稳定裕量有相位裕量和增益裕量两项。

4、锁相环的相位噪声分析

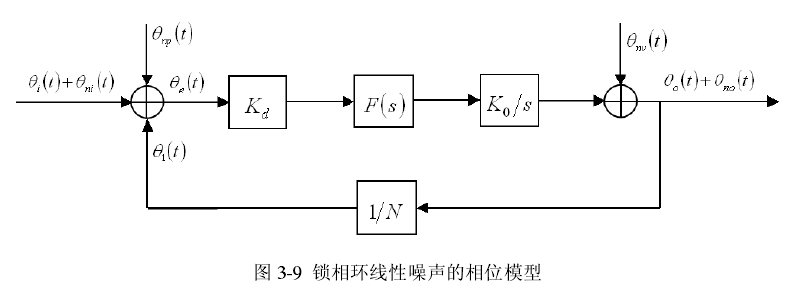

在理想的锁相环中,我们只考虑有用信号的作用,而在实际的应用中,还需要考虑输入噪声和环路内部噪声及各种干扰对环路工作性能的影响。实际环路工作中,环路的各个部件如鉴相器、环路滤波器、分频器、压控振荡器等都会产生噪声。为了便于分析,我们可以将这些噪声看成是由外部输入,并认为锁相环的部件本身为理想无噪声特性。各个部件噪声对环路的作用是不一样的,由此可以将锁相环的相位噪声分为三类。如图 3-9 所示为锁相环的线性噪声相位模型。

如上图3-9所示对三种噪声来进行分析,第一种是输入的等效相位噪声O,(t),是由参考频率进入鉴相器的;第二种为环路底噪声,我们可以把它等效成输入鉴相器的噪声a。(t),它表示的是环路中各个部分形成的高斯白噪声。第三种是VCO自身产生的噪声,也可以把它看作输入VCO的噪声e(t)。在上图中,0.表示参考信号的相位,0。表示锁相环路输出信号的相位,C表示VCO通过N分频之后反馈到鉴相器的信号相位。

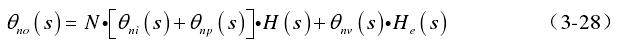

由图 3-9 可以得到锁相环的输出噪声相位为:

在式中,H(s)是闭环传递的函数,具有低通特性;H。(s)是锁相环的误差传递函数,具有高通特性。由上式可得,鉴相器的输入端噪声有低通的特性,VCO内部的噪声有高通的特性。所以,选择合适的环路带宽便可使锁相环总的输出相位噪声达到最小。

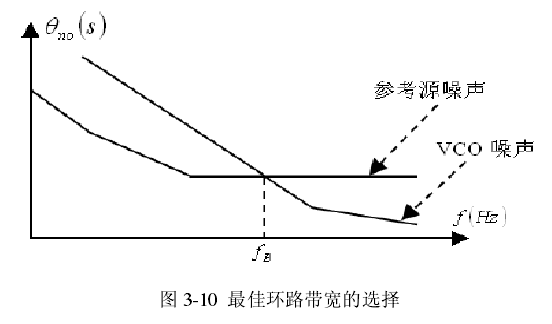

经过对上述各种噪声来源的分析可得,若要减小VCO的输入端相位噪声,环路带宽f。应尽量小;但若要减小VCO内部噪声输出,环路带宽f。取值应尽量大。

所以在输入端的相位噪声以及VCO内部的噪声都不可避免时,应选择合适的环路带宽,通常情况下环路带宽会有一个最佳值使总的输出噪声最小,称此时的环路带宽为最佳环路带宽。在实际应用中,最佳带宽取决于设计方案和芯片选择不同,一般情况下,选择在参考源噪声和VCO噪声两线相交的频率点附近为环路带宽fa。如图3-10为最佳环路带宽的选择示意图。

5、锁相环的杂散分析

PLL 杂散的产生主要有两种途径,一种是鉴相泄露引入的杂散,也是最为常见的一种。为了抑制这种杂散,通常是在环路滤波器的后端再加一级辅助低通滤波器,但是这种方法会因为 LC 或 RC 元件的加入而对锁相环原有的参数产生影响,可能会破坏环路稳定性等性能。为此,通常将辅助滤波器的带宽设计为远大于环路滤波器的带宽,这样对环路滤波器参数的影响就会非常小。另一种杂散的产生是由于外部串扰引入的。对于这种由外部干扰引起的杂散,我们只能采用清楚干扰源或者是阻断干扰源进入的通道。在工程上解决这类杂散最有效的方法就是对电路进行有效的屏蔽以及合理的 PCB 设计.

(未完,待续……)